US 20050116656A1

(19) **United States**

(12) **Patent Application Publication** (10) **Pub. No.: US 2005/0116656 A1**

Shin

(43) **Pub. Date:** **Jun. 2, 2005**

(54) **AMOLED DISPLAY AND DRIVING METHOD THEREOF** (52) **U.S. Cl.** ..... **315/169.3**

(76) Inventor: **Dong-Yong Shin, Seoul (KR)** (57) **ABSTRACT**

Correspondence Address:

**CHRISTIE, PARKER & HALE, LLP**

**PO BOX 7068**

**PASADENA, CA 91109-7068 (US)**

(21) Appl. No.: **10/985,795**

(22) Filed: **Nov. 11, 2004**

(30) **Foreign Application Priority Data**

Nov. 27, 2003 (KR) ..... 2003-84779

**Publication Classification**

(51) **Int. Cl. 7** ..... **G09G 3/10**

An emission control circuit for controlling emission of R, G, B EL elements and method for driving an organic light emitting diode display using the same. An emission control signal generating circuit of a flat panel display includes a plurality of pixels. Each pixel includes a plurality of EL elements, and emission of the elements is controlled by emission control signals. The circuit includes a first signal generating device for generating one of the emission control signals, and a plurality of second signal generating devices for generating other ones of the emission control signals using an output signal of the first signal generating device and an external control signal. The first signal generating device may include a shift register. Each of the plurality of second signal generating devices may include a NAND gate using the external signal and the external control signal, or an inverted signal thereof, as two inputs.

FIG. 1

(PRIOR ART)

FIG. 2

3

FIG.

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 8

FIG. 9

FIG. 10

## AMOLED DISPLAY AND DRIVING METHOD THEREOF

### CROSS-REFERENCE TO RELATED APPLICATION

[0001] This application claims priority to and the benefit of Korean Patent Application No. 2003-84779, filed Nov. 27, 2003, the disclosure of which is incorporated herein by reference in its entirety.

### BACKGROUND OF THE INVENTION

#### [0002] 1. Field of the Invention

[0003] The present invention relates to an organic light emitting diode, and more particularly, to an active matrix organic light emitting diode (AMOLED) display and method for driving the same, which has a simplified configuration of an emission control signal generating circuit.

#### [0004] 2. Description of the Related Art

[0005] In recent years, a liquid crystal display (LCD) and an organic light emitting diode (OLED) display are widely used in a portable information terminal due to advantages of light weight, thin size, and the like. The OLED display is being recognized as a next generation flat panel display because it has brightness and viewing angle characteristics superior to the LCD.

[0006] Typically, in an active matrix organic light emitting diode (AMOLED) display, one pixel includes R, G and B unit pixels, and each of the unit pixels has an electroluminescent (EL) element. The EL elements have R, G, and B organic emission layers interposed between an anode electrode and a cathode electrode thereof, respectively, which emit light in response to the voltage applied to the anode and cathode electrodes.

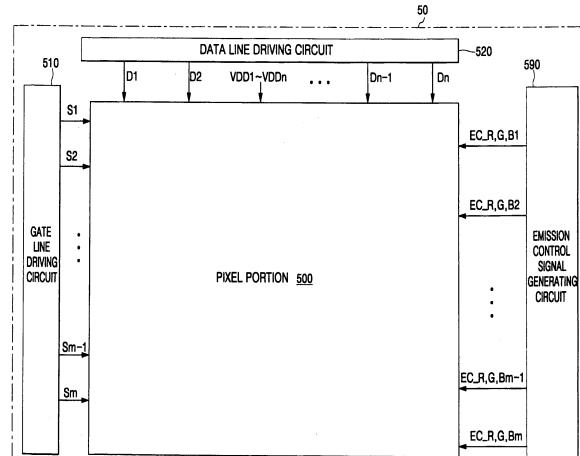

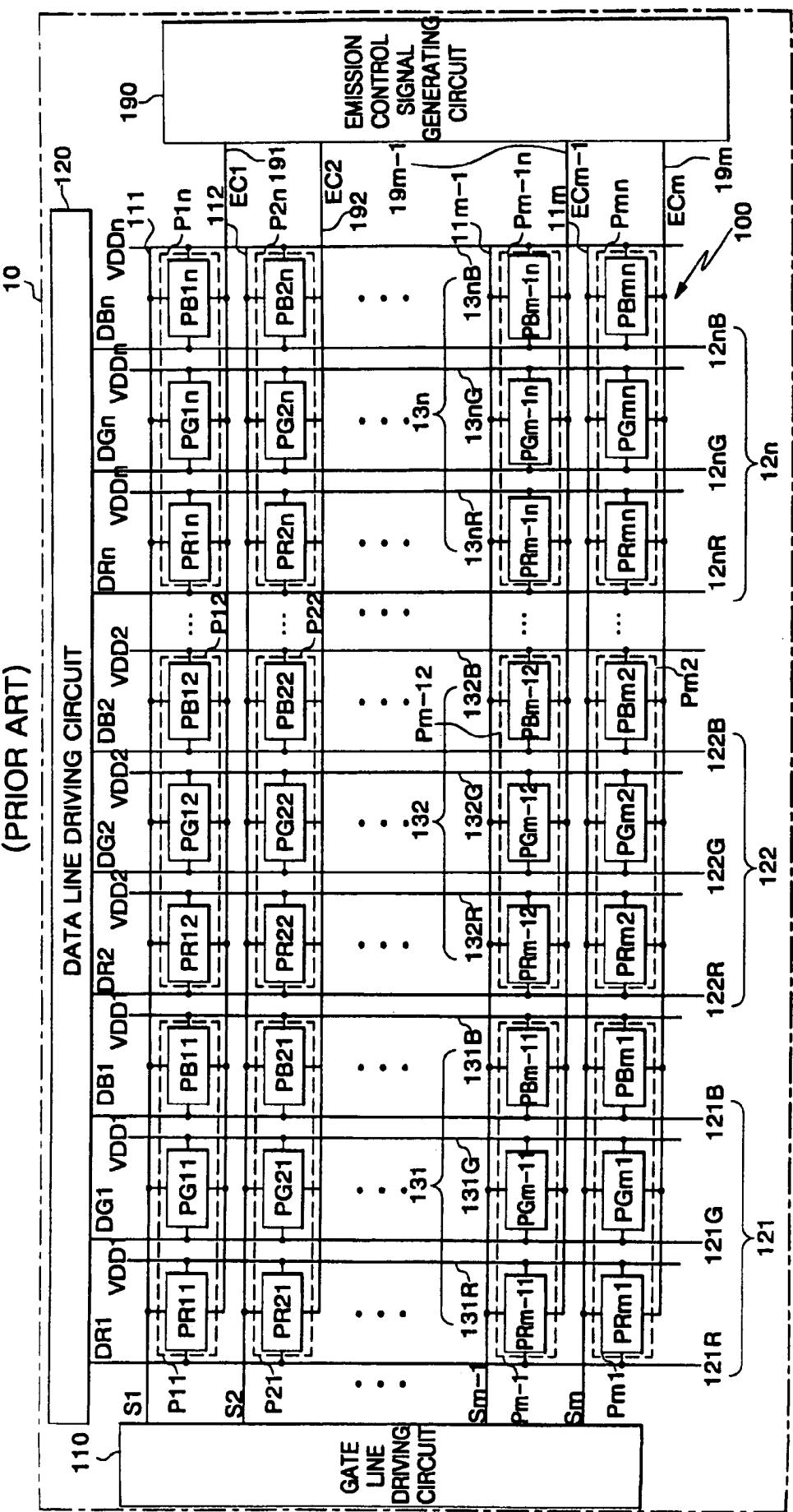

[0007] FIG. 1 shows a configuration of a conventional AMOLED display 10.

[0008] Referring to FIG. 1, the conventional AMOLED display 10 includes a pixel portion 100, a gate line driving circuit 110, a data line driving circuit 120, and an emission control signal generating circuit 190. The pixel portion 100 includes a plurality of gate lines 111-11m provided with scan signals S1-Sm from the gate line driving circuit 110, and a plurality of data lines 121-12n for providing data signals DR1, DG1, DB1-DRn, DGn, DBn from the data line driving circuit 120. In addition, the pixel portion 100 includes a plurality of emission control lines 191-19m for providing emission control signals output from the emission control signal generating circuit 190, and a plurality of power supply lines 131-13n for providing power supply voltage VDD1-VDDn.

[0009] In the pixel portion 100, a plurality of pixels P11-Pmn are arranged in a matrix format, and are connected to the plurality of gate lines 111-11m, the plurality of data lines 121-12n, the plurality of emission control lines 191-19m, and the plurality of power supply lines 131-13n. Each of the pixels P11-Pmn includes three unit pixels, namely R, G, B unit pixels PR11, PG11, PB11-PRmn, PGmn, PBmn, and is connected to corresponding ones of the gate lines, the data lines, the emission control lines and the power supply lines.

[0010] For example, the pixel P11 includes the R unit pixel PR11, the G unit pixel PG11, and the B unit pixel PB11, and is connected to a first gate line 111 for providing a first scan signal S1 among the plurality of gate lines 111-11m, a first data line 121 among the plurality of data lines 121-12n, and a first power supply line 131 among the plurality of power supply lines 131-13n.

[0011] In other words, the R unit pixel PR11 of the pixel P11 is connected to the first gate line 111, the R data line 121R of the first data line 121 provided with the R data signal DR1, and the R power supply line 131R of the first power supply line 131. In addition, the G unit pixel PG11 is connected to the first gate line 111, the G data line 121G of the first data line 121 provided with the G data signal DG1, and the G power supply line 131G of the first power supply line 131. Further, the B unit pixel PB11 is connected to the first gate line 111, the B data line 121B of the first data line 121 provided with the B data signal DB1, and the B power supply line 131B of the first power supply line 131.

[0012] The above-mentioned emission control signal generating circuit 190 includes three emission control signal generating devices for R, G, B, which provide the R, G, B subpixels PR11-PRmn, PG11-PGmn, and PB11-PBmn with emission control signals, respectively, as disclosed in the Japanese Patent Publication No. 2001-60076. Since each of the R, G, B emission control signal generating devices includes a shift register, the number of elements becomes larger and a circuit area also becomes larger. As a result, a failure rate increases and the yield decreases.

### SUMMARY OF THE INVENTION

[0013] An exemplary embodiment according to the present invention provides an organic light emitting diode (OLED) display suitable for fine pitch and a method for driving the same.

[0014] Another exemplary embodiment according to the present invention provides an OLED display having a simplified emission control signal generating circuit and a method for driving the same.

[0015] Yet another exemplary embodiment of the present invention provides an OLED display capable of lengthening the lifetime by adjusting a current flowing through the EL element and a method for driving the same.

[0016] In an exemplary embodiment according to the present invention, an emission control signal generating circuit of a flat panel display is provided. The emission control signal generating circuit includes a plurality of pixels, each said pixel including a plurality of EL elements. Emission of the elements is controlled by a plurality of emission control signals. The circuit includes a first signal generating device for generating one of the plurality of emission control signals as an output signal, and a plurality of second signal generating devices for generating other ones of the plurality of emission control signals using the output signal of the first signal generating device and an external control signal.

[0017] The first signal generating device for generating said one of the plurality of emission control signals may include a shift register. One of the plurality of second signal generating devices may include a NAND gate having the external control signal and the output signal of the first

signal generating device as two inputs, and another one of the plurality of second signal generating devices may include a NAND gate having an inverted signal of the external control signal and the output signal of the first signal generating device as two inputs.

[0018] One of the plurality of second signal generating devices may include a first transfer gate for providing the output signal of the first signal generating device as one of said other ones of the plurality of emission control signals using the external control signal having a first level and an inverted signal of the external control signal having a second level, and a second transfer gate for allowing said one of said other ones of the plurality of emission control signals to have the second level using the external control signal having the second level and the inverted signal of the external control signal having the first level. Another one of the plurality of second signal generating devices may include a third transfer gate for providing the output signal of the first signal generating device as another one of said other ones of the plurality of emission control signals using the external control signal having the second level and the inverted signal of the external control signal having the first level, and a fourth transfer gate for allowing said another one of said other ones of the plurality of emission control signals to have the second level using the external control signal having the first level and the inverted signal of the external control signal having the second level.

[0019] The plurality of EL elements may be sequentially driven per each of subframes that form one frame and may be in a black color state, or one of the plurality of EL elements may be driven again, during one of the plurality of subframes.

[0020] In another exemplary embodiment according to the present invention, an emission control signal generating circuit of an organic light emitting diode display including a plurality of pixels is provided. Each said pixel includes R, G, B EL elements, and emission of said elements is controlled by R, G, B emission control signals. The circuit includes a shift register for generating the G emission control signal as an output signal. The circuit also includes a first NAND gate for generating the R emission control signal using the output signal of the shift register and an external control signal as two inputs. An inverting gate inverts the external control signal to generate an inverted external control signal, and a second NAND gate generates the B emission control signal using the inverted external control signal and the output signal of the shift register as two inputs.

[0021] In yet another exemplary embodiment according to the present invention, an emission control signal generating circuit of an organic light emitting diode display including a plurality of pixels is provided. Each said pixel includes R, G, B EL elements, and emission of said elements is controlled by R, G, B emission control signals. The circuit includes an inverting gate for inverting an external control signal to generate an inverted external control signal, and a shift register for generating the G emission control signal as an output signal. A first transfer gate transfers the output signal of the shift register as the R emission control signal using the inverted external control signal and the external control signal. A second transfer gate grounds the R emission control signal using the inverted external control signal

and the external control signal. A third transfer gate transfers the output signal of the shift register as the B emission control signal using the inverted external control signal and the external control signal. A fourth transfer gate grounds the B emission control signal using the inverted external control signal and the external control signal.

[0022] In yet another exemplary embodiment according to the present invention, an organic light emitting diode display includes a plurality of gate lines, a plurality of data lines, a plurality of emission control lines, a plurality of power supply lines, and a pixel portion including a plurality of pixels. Each said pixel is connected to a corresponding said gate line, a corresponding said data line, a corresponding said emission control line, and a corresponding said power supply line. A gate line driving circuit supplies the plurality of gate lines with a plurality of scan signals, a data line driving circuit sequentially supplies the plurality of data lines with R, G, B data signals, and an emission control signal generating circuit supplies the plurality of emission control lines with a plurality of emission control signals. Each said pixel includes R, G, B EL elements, which sequentially emit light based on the emission control signals per each of a plurality of subframes that form one frame. The emission control signal generating circuit includes a first signal generating device for generating one of the plurality of emission control signals as an output signal, and a plurality of second signal generating devices for generating other ones of the plurality of emission control signals using the output signal of the first signal generating device and an external control signal.

[0023] Each pixel may further include at least one switching transistor for switching the data signal, at least one driving transistor for providing the R, G, B EL elements with a driving current corresponding to the data signal, and a capacitor for storing the data signal, and a sequential control device for controlling sequential driving of the R, G, B EL elements.

[0024] The sequential control device may include first, second and third P-type thin film transistors, each said thin film transistor including a gate to which a corresponding said emission control signal is applied, a source connected to the driving device in common, and a drain connected to a corresponding one of the R, G, B EL elements. Alternatively, the sequential control device may include a first N-type thin film transistor, a first P-type thin film transistor and a second N-type thin film transistor, each said thin film transistor including a gate to which a corresponding said emission control signal is applied, a source connected to the driving device in common, and a drain connected to a corresponding one of the R, G, B EL elements.

[0025] In yet another exemplary embodiment according to the present invention, an organic light emitting diode display includes a plurality of gate lines, a plurality of data lines, a plurality of emission control lines, a plurality of power supply lines, and a pixel portion including a plurality of pixels, each said pixel being connected to a corresponding said gate line, a corresponding said data line, a corresponding said emission control line and a corresponding said power supply line. A gate line driving circuit supplies the plurality of gate lines with a plurality of scan signals, a data line driving circuit sequentially supplies the plurality of data lines with R, G, B data signals, and an emission control

signal generating circuit supplies the plurality of emission control lines with R, G, B emission control signals. Each said pixel includes R, G, B EL elements, which sequentially emit light based on the R, G, B emission control signals per each of a plurality of subframes that form one frame. The emission control signal generating circuit includes a shift register for generating the G emission control signal as an output signal, and a first NAND gate for generating the R emission control signal using the output signal of the shift register and an external control signal as two inputs. An inverting gate inverts the external control signal to generate an inverted external control signal, and a second NAND gate generates the B emission control signal using the inverted external control signal and the output signal of the shift register as two inputs.

[0026] In yet another exemplary embodiment according to the present invention, an organic light emitting diode display includes a plurality of gate lines, a plurality of data lines, a plurality of emission control lines, a plurality of power supply lines, and a pixel portion including a plurality of pixels, each said pixel being connected to a corresponding said gate line, a corresponding said data line, a corresponding said emission control line and a corresponding said power supply line. A gate line driving circuit supplies the plurality of gate lines with a plurality of scan signals, a data line driving circuit sequentially supplies the plurality of data lines with R, G, B data signals, and an emission control signal generating circuit supplies the plurality of emission control lines with R, G, B emission control signals. Each said pixel includes R, G, B EL elements, which sequentially emit light based on the R, G, B emission control signals per each of a plurality of subframes that form one frame. The emission control signal generating circuit includes an inverting gate for inverting an external control signal to generate an inverted external control signal, and a shift register for generating the G emission control signal as an output signal. A first transfer gate transfers the output signal of the shift register as the R emission control signal using the inverted external control signal and the external control signal. A second transfer gate grounds the R emission control signal using the inverted external control signal and the external control signal. A third transfer gate transfers the output signal of the shift register as the B emission control signal using the inverted external control signal and the external control signal. A fourth transfer gate grounds the B emission control signal using the inverted external control signal and the external control signal.

[0027] In yet another exemplary embodiment according to the present invention, a method for driving an organic light emitting diode display including a plurality of pixels is provided. Each said pixel includes R, G, B EL elements, and emission of said elements is controlled by R, G, B emission control signals. The G emission control signal is generated during a first subframe among a plurality of subframes that form one frame to emit the G EL element, and the R emission control signal is generated using the G emission control signal during a second said subframe to emit the R EL element. The B emission control signal is generated using the G emission control signal during a third said subframe to emit the B EL element. The EL elements are maintained to be a black color during a rest subframe among the plurality of subframes.

[0028] In yet another exemplary embodiment of the present invention, a method for driving an organic light emitting diode display including a plurality of pixels is provided. Each said pixel includes R, G, B EL elements, and emission of each said element is controlled by R, G, B emission control signals. The G emission control signal is generated during a first subframe among a plurality of subframes that form one frame to emit the G EL element, and the R emission control signal is generated using the G emission control signal during a second said subframe to emit the R EL element. The B emission control signal is generated using the G emission control signal during a third said subframe to emit the B EL element. One of the R, G, B EL elements is emitted during a rest subframe among the plurality of subframes.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0029] The above and other features of the present invention will become more apparent to those of ordinary skill in the art with the description in detail of certain exemplary embodiments thereof with reference to the attached drawings in which:

[0030] FIG. 1 shows a configuration of a conventional organic light emitting diode (OLED) display.

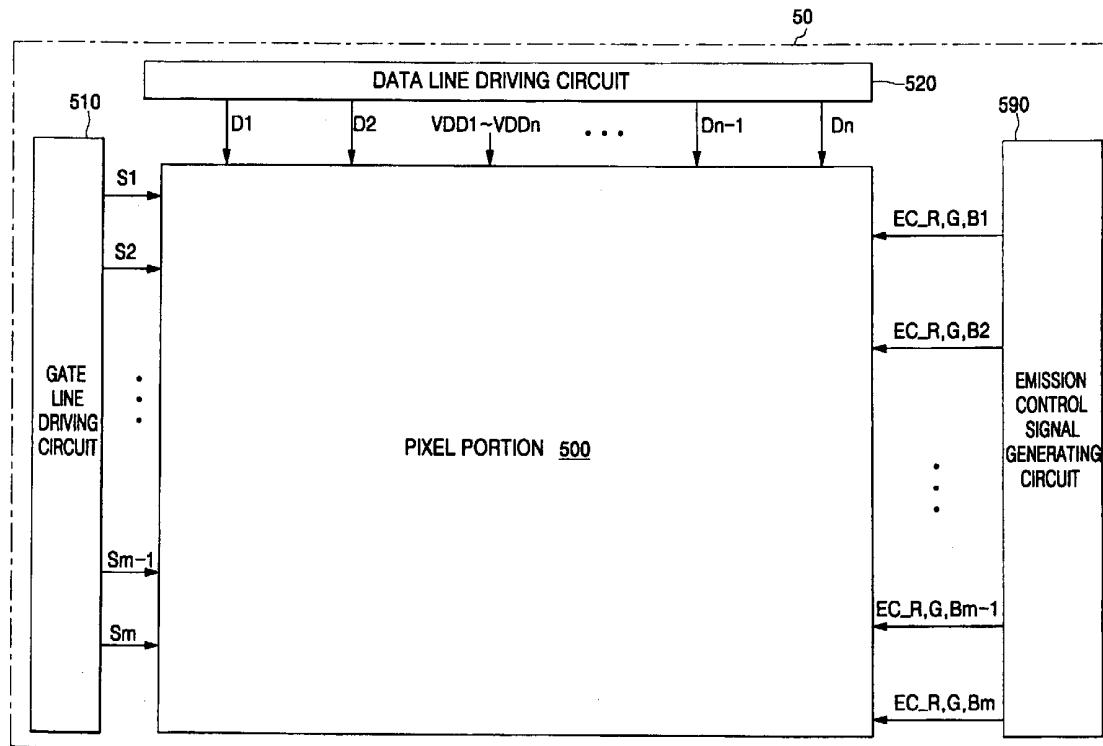

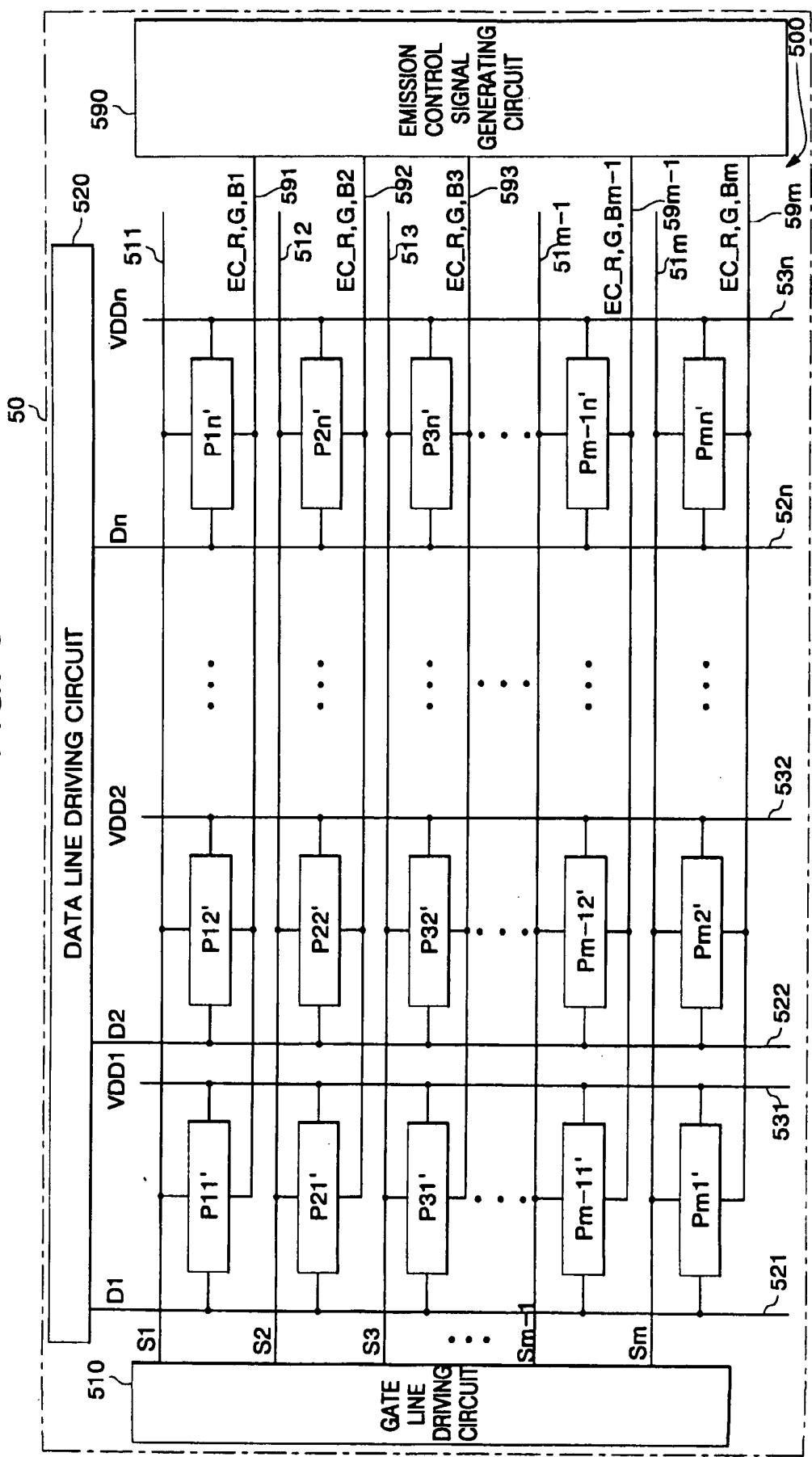

[0031] FIG. 2 is a block diagram of a sequential driving OLED display in accordance with an exemplary embodiment of the present invention.

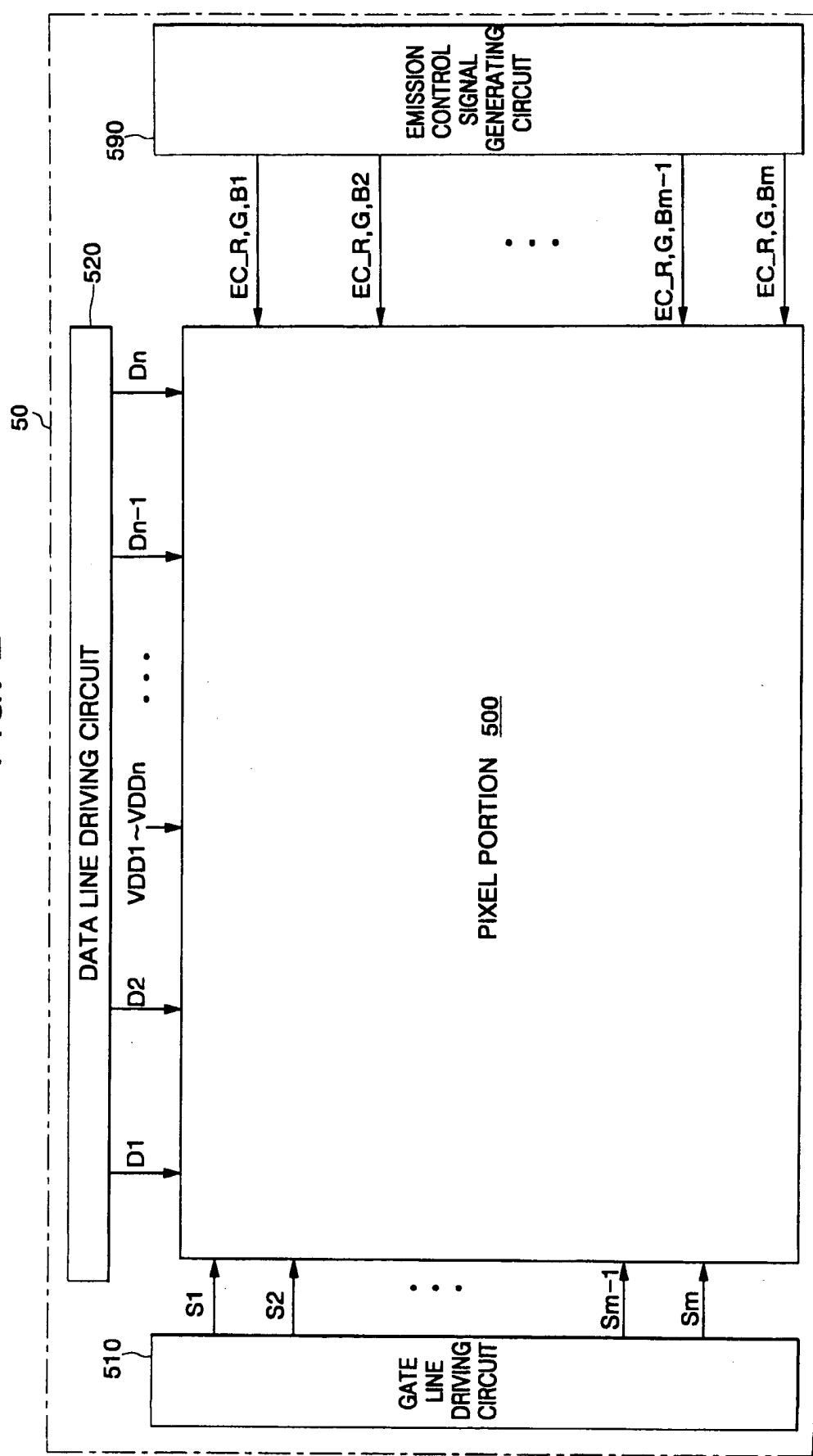

[0032] FIG. 3 is a block diagram of the OLED display of FIG. 2, which shows a pixel portion in more detail.

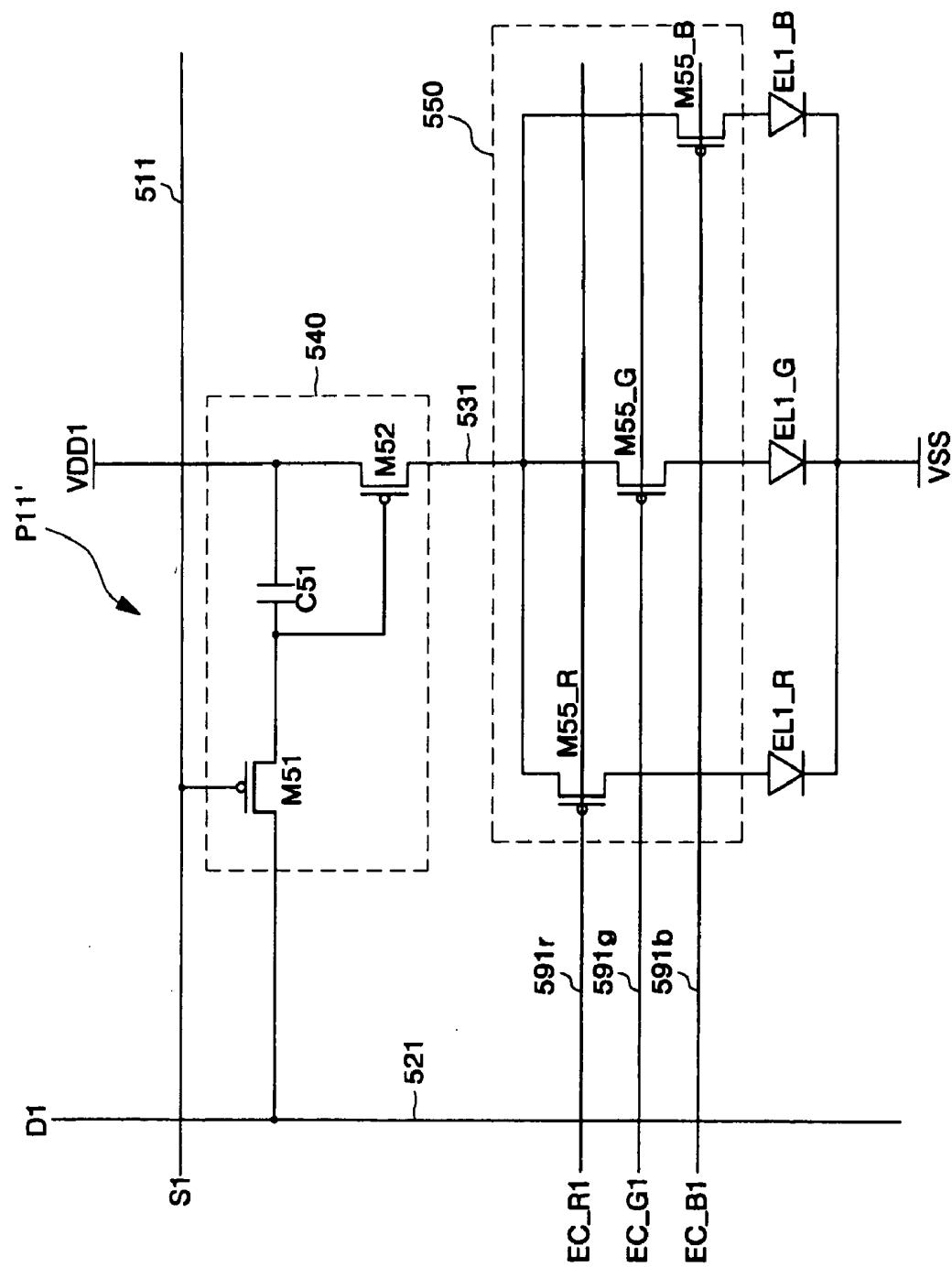

[0033] FIG. 4 shows a pixel circuit in the OLED display of FIG. 3.

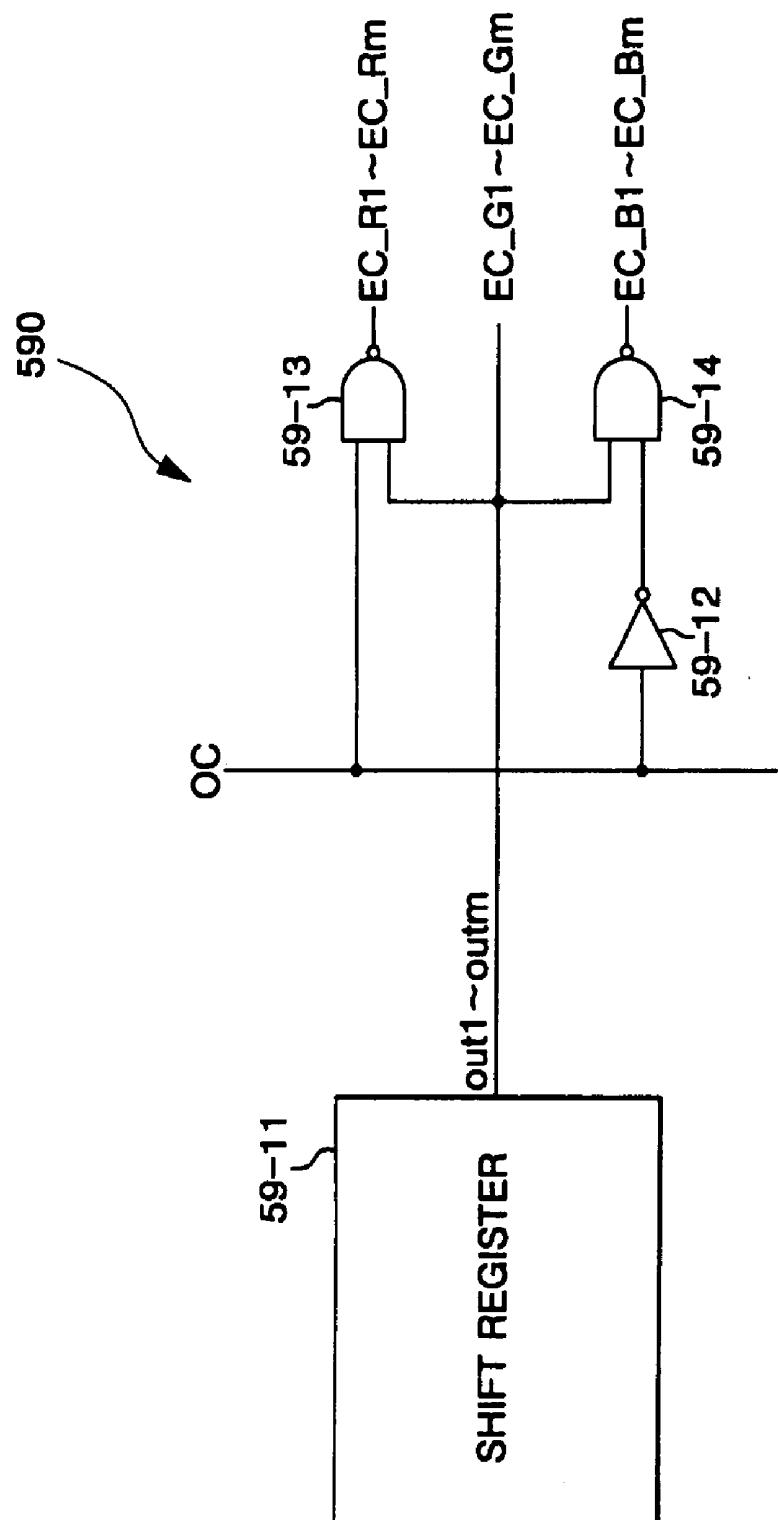

[0034] FIG. 5 shows an emission control signal generating circuit in the OLED display in accordance with a first exemplary embodiment of the present invention.

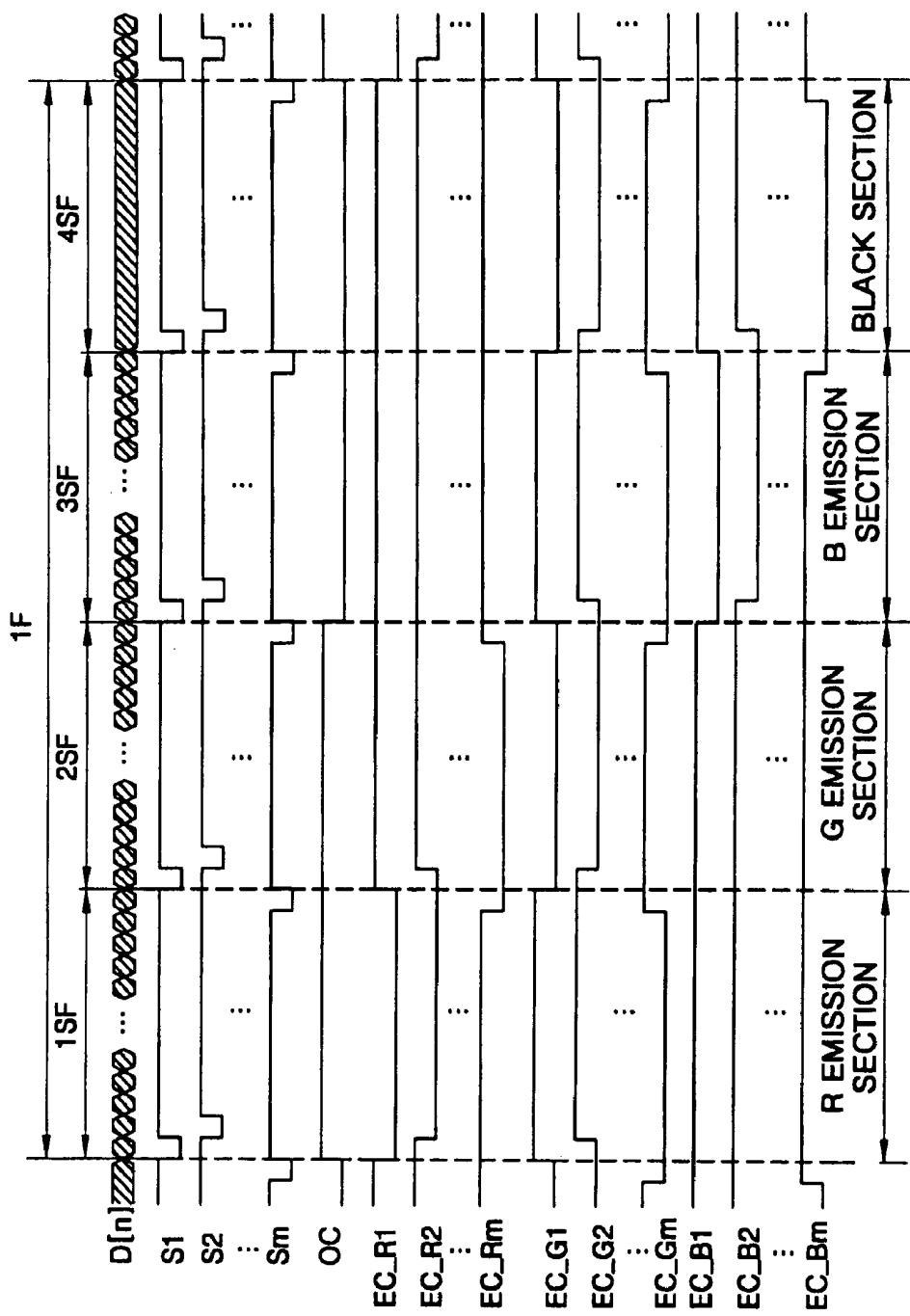

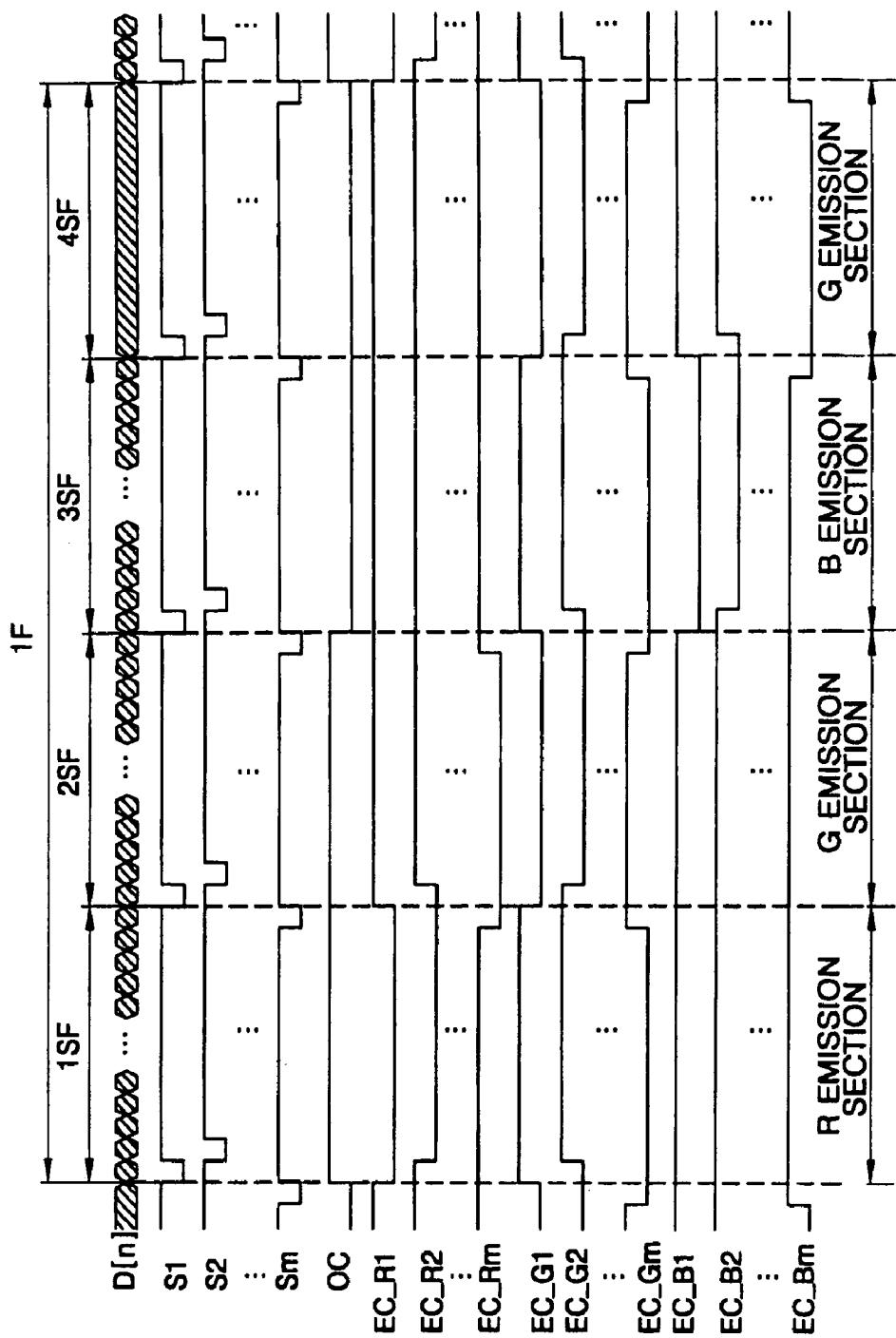

[0035] FIG. 6 shows operating waveforms of an OLED display using the emission control signal generating circuit of FIG. 5.

[0036] FIG. 7 shows other operating waveforms of an OLED display using the emission control signal generating circuit of FIG. 5.

[0037] FIG. 8 shows a pixel circuit of an OLED display in accordance with a second exemplary embodiment of the present invention.

[0038] FIG. 9 shows an emission control signal generating circuit of an OLED display in accordance with a second exemplary embodiment of the present invention.

[0039] FIG. 10 shows operating waveforms of an OLED display using the emission control signal generating circuit of FIG. 9.

#### DETAILED DESCRIPTION

[0040] The present invention will now be described more fully hereinafter with reference to the accompanying drawings, in which exemplary embodiments of the invention are shown. This present invention may, however, be embodied in different forms and should not be construed as limited to the embodiments set forth herein. Rather, these embodiments are provided so that this disclosure will be thorough

and complete, and will fully convey the scope of the invention to those skilled in the art. In the drawings, the thickness of layers and regions are exaggerated for clarity. Like numbers refer to like elements throughout the specification.

[0041] Referring to FIG. 2, an OLED display 50 includes a pixel portion 500, a gate line driving circuit 510, a data line driving circuit 520, and an emission control signal generating circuit 590. The gate line driving circuit 510 sequentially generates scan signals S1-Sm to gate lines of the pixel portion 500 during one frame. The data line driving circuit 520 sequentially provides data lines of the pixel portion 500 with R, G, B data signals D1-Dn each time the scan signal is applied to the pixel portion during one frame. The emission control signal generating circuit 590 sequentially supplies emission control lines 591-59m (shown in FIG. 3) of the pixel portion 500 with emission control signals (EC\_R, G, B1) to (EC\_R, G, Bm) for controlling emission of the R, G, B EL elements each time the scan signal is applied to the pixel portion during one frame.

[0042] Referring to FIG. 3, the pixel portion 500 includes a plurality of gate lines 511-51m provided with scan signals S1-Sm, respectively, from the gate line driving circuit 510, a plurality of data lines 521-52n provided with data signals D1-Dn, respectively, from the data line driving circuit 520, a plurality of emission control lines 591-59m provided with emission control signals EC\_R, G, B1 to EC\_R, G, Bm, respectively, from the emission control signal generating circuit 590, and a plurality of power supply lines 531-53n for providing power supply voltages VDD1-VDDn, respectively.

[0043] The pixel portion 500 further includes a plurality of pixels P11'-Pmn' arranged in a matrix format, which are connected to the plurality of gate lines 511-51m, the plurality of data lines 521-52n, the plurality of emission control lines 591-59m, and the plurality of power supply lines 531-53n. Each of the pixels P11'-Pmn' is connected to a corresponding one of the plurality of gate lines 511-51m, a corresponding one of the plurality of data lines 521-52n, a corresponding one of the plurality of emission control lines 591-59m, and a corresponding one of the plurality of power supply lines 531-53n.

[0044] For example, the pixel P11' is connected to a first gate line 511 for providing a first scan signal S1 among the plurality of gate lines 511-51m, a first data line 521 for providing a first data signal D1 among the plurality of data lines 521-52n, a first emission control line 591 for providing a first emission control signal EC\_R, G, B1 among the plurality of emission control lines 591-59m, and a first power supply line 531 among the plurality of power supply lines 531-53n.

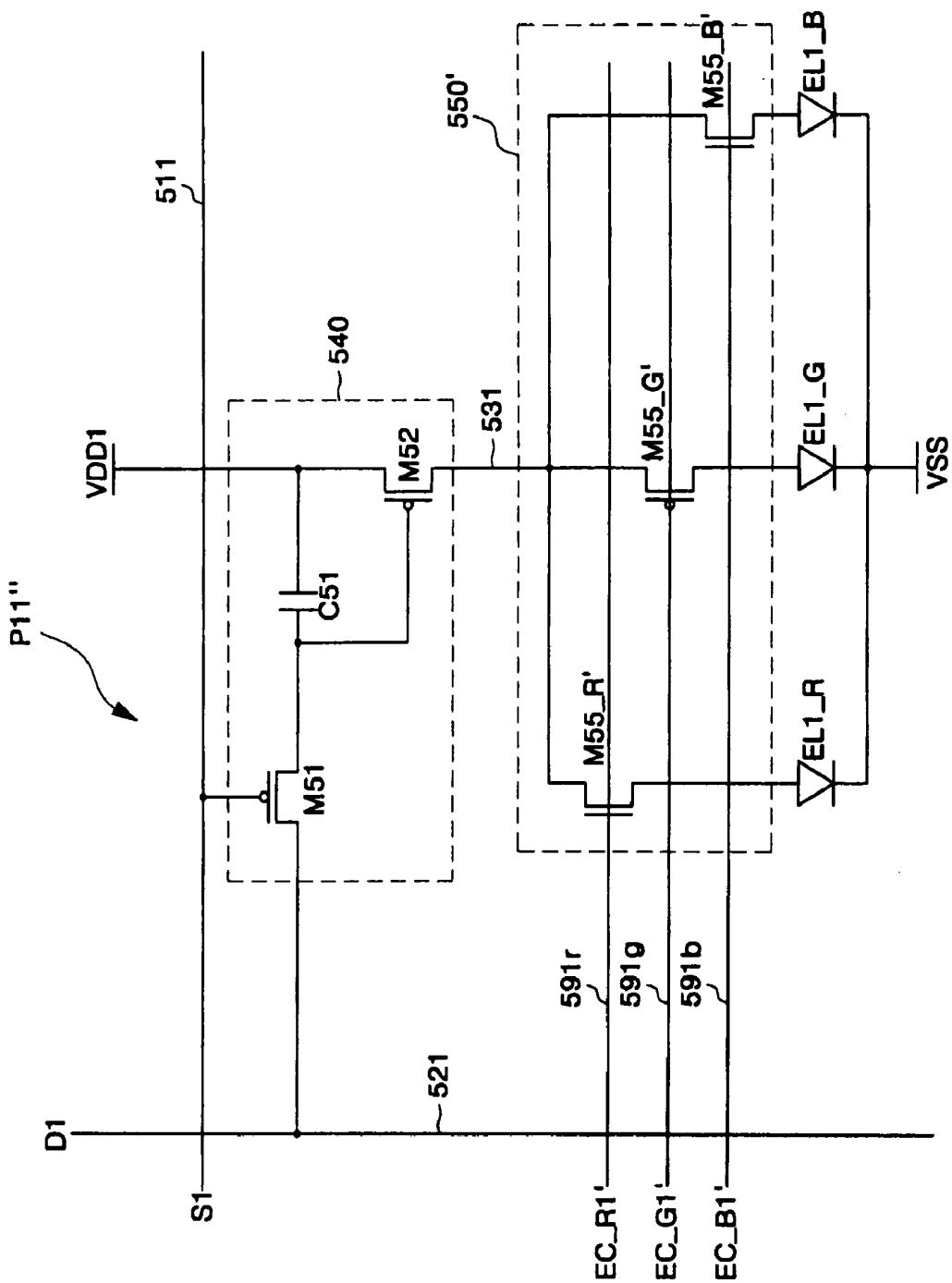

[0045] FIG. 4 shows a pixel circuit for one pixel in a sequential driving OLED display in accordance with a first exemplary embodiment of the present invention, which corresponds to a case for the one pixel P11' among the plurality of pixels.

[0046] Referring to FIG. 4, the pixel P11' includes a gate line 511, a data line 521, three emission control lines 591<sub>r</sub>, 591<sub>g</sub>, 591<sub>b</sub>, a power supply line 531, and R, G, B EL elements EL1\_R, EL1\_G, EL1\_B for emitting R, G, B colors, respectively, as display elements.

[0047] In addition, the pixel P11' includes an active element for driving the R, G, B EL elements EL1\_R, EL1\_G, EL1\_B in a time-sharing and sequential manner. The active element has a driving device 540 for supplying the R, G, B EL elements EL1\_R, EL1\_G, EL1\_B with a driving current corresponding to the R, G, B data signal D1 (DR1, DG1, DB1) each time the scan signal S1 is applied thereto, and a sequential control device 550 for sequentially providing the R, G, B EL elements EL1\_R, EL1\_G, EL1\_B with a driving current corresponding to the R, G, B data signals (DR1, DG1, DB1) from the driving device 540 based on the emission control signals EC\_R1, EC\_G1, EC\_B1.

[0048] The driving device 540 includes a switching transistor M51, a driving transistor M52, and a capacitor C51 connected between a gate and a source of the driving transistor M52. The scan signal S1 is applied to the gate of the switching transistor M51 from the gate line 511, and R, G, B data signals DR1, DG1, DB1 are sequentially applied to the source of the switching transistor M51 from the data line 521. In addition, the gate of the driving transistor M52 is connected to the drain of the switching transistor M51. Further, a power supply voltage VDD1 is applied to the source of the driving transistor M52 from the power supply line 531, and the drain of the driving transistor M52 is connected to the sequential control device 550.

[0049] The sequential control device 550 is connected between the drain of the driving transistor M52 of the driving device 540 and anodes of the R, G, B EL elements EL1\_R, EL1\_G, EL1\_B as display elements, and sequentially controls the driving of the R, G, B EL elements EL1\_R, EL1\_G, EL1\_B based on the emission control signals EC\_R1, EC\_G1, EC\_B1.

[0050] The sequential control device 550 has a first P-type thin film transistor M55\_R for providing the R EL element (EL1\_R) with the driving current corresponding to the R data signal from the driving transistor M52 in response to the first emission control signal EC\_R1 applied to its gate, which is connected between the driving device 540 and the R EL element EL1\_R.

[0051] The sequential control device 550 also includes a second P-type thin film transistor M55\_G for providing the G EL element EL1\_G with the driving current corresponding to the G data signal from the driving transistor M52 in response to the second emission control signal EC\_G1 applied to its gate, which is connected between the driving means 540 and the G EL element EL1\_G.

[0052] Further, the sequential control device 550 includes a third P-type thin film transistor M55\_B for providing the B EL element EL1\_B with the driving current corresponding to the B data signal from the driving transistor M52 in response to the third emission control signal EC\_B1 applied to its gate, which is connected between the driving device 540 and the B EL element EL1\_B.

[0053] The pixel circuit having the above-mentioned configuration allows R, G, B EL elements EL1\_R, EL1\_G, EL1\_B to share the one driving device 540, so that these R, G, B EL elements EL1\_R, EL1\_G, EL1\_B are sequentially driven in order to have the pixel P11' display a desired color by driving three R, G, B EL elements EL1\_R, EL1\_G, EL1\_B during one frame. In other words, one frame is divided into three sub frames, and R, G, B emission control

signals corresponding to the sub frames are applied to the sequential control device 550 so as to perform sequential emission of the R, G, B EL elements EL1\_R, EL1\_G, EL1\_B. As a result, the R, G, B EL elements EL1\_R, EL1\_G, EL1\_B are driven in a time-sharing and sequential manner during one frame to thereby allow the pixel P11' to implement the desired color.

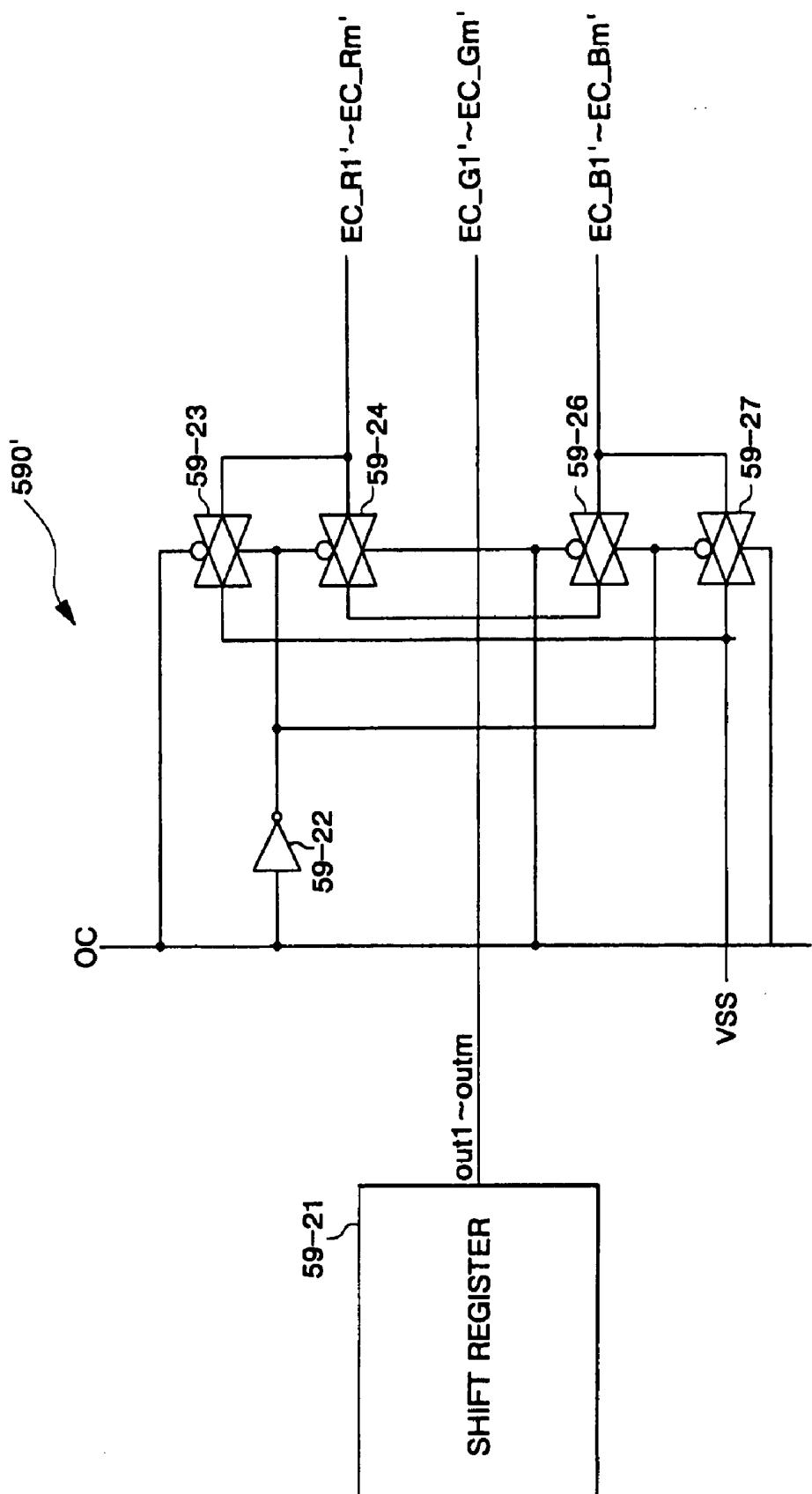

[0054] Referring to FIG. 5, the emission control signal generating circuit 590 includes a shift register 59-11 for generating the emission control signals EC\_G1-EC\_Gm for controlling the emission of the G EL elements. The emission control signal generating circuit 590 also includes a first NAND gate 59-13 that uses the output control signal OC and the output signal of the shift register 59-11 (out1-outm) as two inputs to generate the emission control signals EC\_R1-EC\_Rm for controlling the emission of the R EL elements. Further, the emission control signal generating circuit 590 includes an inverter 59-12 for inverting the output control signal OC, and a second NAND gate 59-14 that uses the output signal of the shift register 59-11 (out1-outm) and the output of the inverter 59-12 as two inputs to generate the emission control signals EC\_B1-EC\_Bm for controlling the emission of the B EL elements.

[0055] Waveform having the same duty ratio as the G emission control signals EC\_G1-EC\_Gm as shown in FIG. 6 for controlling the G EL elements is supplied to the shift register 59-11 as an input signal, and the shift register 59-11 delays the input signal for a predetermined time to generate the G emission control signals EC\_G1-EC\_Gm.

[0056] Hereinafter, a method for driving the OLED display having the above-mentioned configuration in accordance with the present invention will be described with reference to FIG. 6.

[0057] In exemplary embodiments of the present invention, one frame is divided into four subframes, and a scan signal is applied to the respective gate lines from the gate line driving circuit 510 during each subframe, so that 4m scan signals are applied thereto during one frame. When the scan signal S1 is applied to the first gate line 511 during the first subframe 1SF, the switching transistor M51 is turned on to allow the R data signal DR1 to be applied from the data line 521 to the driving transistor M52.

[0058] In this case, the R emission control signal EC\_R1 is generated by the NAND gate 59-13 using the output control signal OC and the G emission control signal EC\_G1 as two inputs in the emission control signal generating circuit 590. As a result, when the emission control signal EC\_R1 is applied to the sequential control device 550 to control the R EL element EL\_R of each of the pixels P11'-P1n' connected to the first gate line 511 through the emission control line 591, the thin film transistor M55\_R is turned on to allow the driving current corresponding to the R data signals DR1-DRn to flow, respectively, through the R EL elements of the pixels to be driven.

[0059] When the second scan signal S1 is applied to the first gate line 511 during the second subframe 2SF of the first frame 1F, the G data signals DG1-DGn are applied to the driving transistors M52 of the pixels P11'-P1n' through the data line 521-52n, respectively. In this case, the G emission control signal EC\_G1 generated by the shift register 59-11 in the emission control signal generating circuit 590 is provided through the emission control line 591.

[0060] As a result, when the emission control signal EC\_G1 is applied to the sequential control device 550 to control the G EL element EL\_G of each of the pixels P11'-P1n' connected to the first gate line 511, the thin film transistors M55\_G in the pixels are turned on to allow the driving current corresponding to the G data signals DG1-DGn to flow, respectively, through the G EL elements to be driven.

[0061] When the third scan signal S1 is applied to the first gate line 511 during the third subframe 3SF of the first frame 1F, the B data signals DB1-DBn are applied to the driving transistors M52 of the pixels P11'-P1n' through the data line 521-52n, respectively. In this case, the B emission control signal EC\_B1 is generated in the emission control signal generating circuit 590 by the NAND gate 59-14 using its two inputs of the output control signal OC and the output signal out1 of the shift register 59-11 to the emission control line 591b.

[0062] As a result, when the emission control signal EC\_B1 is applied to the sequential control device 550 to control the B EL element EL\_B in each of the pixels P11'-P1n' connected to the first gate line 511, the thin film transistors M55\_B of the pixels are turned on to allow the driving current corresponding to the B data signals DB1-DBn to flow, respectively, through the B EL elements to be driven.

[0063] During the fourth subframe 4SF of the first frame, in response to the emission control signals EC\_R1 and EC\_B1 generated by the emission control signal generating circuit 590, the R and B EL elements are turned off, and a driving current corresponding to black data flows through the G EL element to thereby display a black color during the fourth subframe.

[0064] When the above-mentioned operation is repeated per each subframe of one frame to apply the scan signal to the m<sup>th</sup> gate line 51m, the R, G, B data signals (DR1-DRn), (DG1-DGn), (DB1-DBn) are sequentially applied to the data lines 521-52n, and the emission control signals (EC\_Rm, EC\_Gm, EC\_Bm) are sequentially generated by the emission control signal generating circuit 590 to the sequential control device 550, which sequentially controls the R, G, B EL elements of the pixel Pm1'-Pmn' connected to the m<sup>th</sup> gate line 51m through the emission control lines 59mr, 59mg, 59mb. As a result, the thin film transistors M55\_R, M55\_G, M55\_B are sequentially turned on to thereby allow driving currents corresponding to the R, G, B data signals DR1-DRn, DG1-DGn, DB1-DBn to sequentially flow through the R, G, B EL elements to be driven.

[0065] Therefore, one frame is divided into four subframes, and the R, G, B EL elements are sequentially controlled by the emission control signals generated from the emission control signal generating circuit 590 during the first to third subframes, and are controlled to have a black color in the fourth subframe in the described embodiment of the present invention.

[0066] As such, whenever the scan signals S1-Sm are applied per each subframe of the one frame, the data signals DR1-DRn, DG1-DGn, DB1-DBn are sequentially applied to the data lines, respectively, so that the R, G, B EL elements EL\_R, EL\_G, EL\_B of the pixel Pm1'-Pmn' are sequentially driven in a time-sharing manner. In this case, the R, G, B EL

elements are sequentially driven, however, such sequential driving takes place within a very short time period, so that people may perceive these R, G, B EL elements as being simultaneously driven to allow the image therefrom to be naturally displayed.

[0067] The pixel circuit of the present invention allows R, G, B EL elements EL1\_R, EL1\_G, EL1\_B of the pixel P11 to share one driving device 540, which leads to simplify the circuit configuration. In addition, three emission control signals for R, G, B are generated from one shift register to thereby reduce the circuit area.

[0068] The output control signal OC is supplied from an external source to the emission control signal generating circuit 590, and controls the R, G, B emission control signals to be output from the emission control signal generating circuit.

[0069] In accordance with a method for driving the OLED display of the present invention, as shown in FIG. 6, one frame is divided into four subframes, and R, G, B EL elements are sequentially driven by the R, G, B emission control signals generated from the emission control signal generating circuit 590 per each of the three subframes, and the R and B EL elements are put in a non-emission state and the G EL element to be in a black color state by the R, G, B emission control signals generated from the emission control signal generating circuit during the rest subframe.

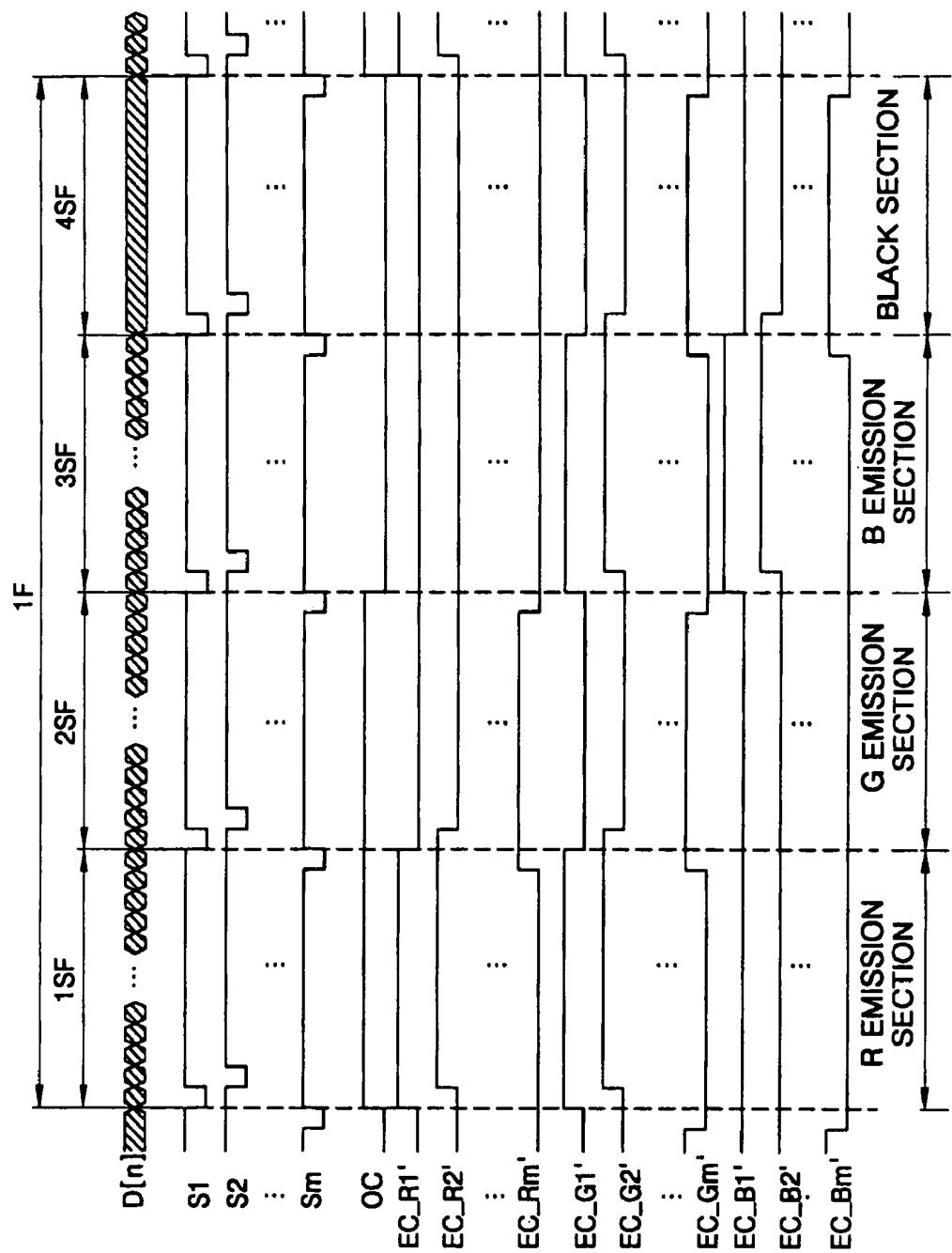

[0070] In accordance with another method for driving the OLED display of the present invention, as shown in FIG. 7, one frame is divided into four subframes, and R, G, B EL elements are sequentially driven by the R, G, B emission control signals generated from the emission control signal generating circuit 590 per each of the three subframes, and the emission control signal generating circuit 590 drives again one of the R, G, B EL elements, for example, the G EL element during the rest subframe. As such, one EL element, for example, the G EL element having a relatively high driving current among the R, G, B EL elements is driven by half of the driving current in the second subframe and by half in the fourth subframe, so that it is driven twice, which reduces the current amount flowing through the G EL element during one subframe to thereby reduce the power consumption and lengthen the lifetime thereof.

[0071] FIG. 8 shows a pixel circuit of a sequential driving OLED display in accordance with a second exemplary embodiment of the present invention, which corresponds to a case for one pixel P11" among the plurality of pixels. The pixel P11" of FIG. 8, for example, may be used in the OLED display that has substantially the same configuration as the OLED display 50 of FIGS. 2 and 3 in a pixel portion which is substantially the same as the pixel portion 500.

[0072] Referring to FIG. 8, the configuration of the pixel circuit in accordance with the second exemplary embodiment of the present invention is almost the same as the pixel circuit of the first embodiment. A difference therebetween is as follows. A sequential control device 550 includes a first N-type thin film transistor M55\_R' connected between a driving device 540 and the R EL element EL1\_R and provides a driving current corresponding to the R data signal from the driving transistor M52 to the R EL element EL1\_R in response to the first emission control signal EC\_R1' applied to its gate. In addition, a second P-type thin film

transistor M55\_G' connected between the driving device 540 and the G EL element EL1\_G provides a driving current corresponding to the G data signal from the driving transistor M52 to the G EL element EL1\_G in response to the second emission control signal EC\_G1' applied to its gate. Further, a third N-type thin film transistor M55\_B' connected between the driving device 540 and the B EL element EL1\_B provides a driving current corresponding to the B data signal from the driving transistor M52 to the B EL element EL1\_B in response to the third emission control signal EC\_B1' applied to its gate.

[0073] FIG. 9 shows an emission control signal generating circuit 590' of an OLED display in accordance with a second exemplary embodiment of the present invention. The emission control signal generating circuit 590' of FIG. 9, for example, may be used in an OLED display which is substantially the same as the OLED display 50 of FIGS. 2 and 3.

[0074] Referring to FIG. 9, the emission control signal generating circuit in accordance with the second exemplary embodiment includes a shift register 59-21 that generates emission control signals EC\_G1'-EC\_Gm' for controlling the emission of the G EL elements, and an inverting gate 59-22 for inverting the output control signal OC.

[0075] In addition, the emission control signal generating circuit 590' further includes a first transfer gate 59-24 for transferring the output signals out1-outm (i.e., EC\_G1'-EC\_Gm') of the shift register 59-21 in response to the output signal of the inverting gate 59-22 and the external control signal as the R emission control signals EC\_R1'-EC\_Rm', and a second transfer gate 59-23 for grounding the R emission control signals EC\_R1'-EC\_Rm' in response to the output signal of the inverting gate 59-22 and the output control signal OC.

[0076] The emission control signal generating circuit 590' further includes a third transfer gate 59-26 for transferring the output signals out1-outm (i.e., EC\_G1'-EC\_Gm') of the shift register 59-21 in response to the output signal of the inverting gate 59-22 and the output control signal OC as the B emission control signals EC\_B1'-EC\_Bm', and a fourth transfer gate 59-27 for grounding the B emission control signals EC\_B1'-EC\_Bm' in response to the output signal of the inverting gate 59-22 and the output control signal OC.

[0077] Waveform having the same duty ratio as the G emission control signals EC\_G1'-EC\_Gm' as shown in FIG. 9 for controlling the G EL elements is supplied to the shift register 59-21 as an input signal, and the shift register 59-21 delays the input signal for a predetermined time to generate the G emission control signals EC\_G1'-EC\_Gm'. The ground voltage Vss may be separately provided, or it may be the ground voltage used for the shift register 59-21 or the inverting gate 59-22.

[0078] The emission control circuit of the OLED display in accordance with the second exemplary embodiment of the present invention places the emission control signal of the corresponding EL element in a ground level when the corresponding EL element is in a non-emission state, however, it may place the emission control signal of the EL element of the non-emission state in a level of power supply voltage (VDD) when all of the transistors in the sequential control device are P-type thin film transistors as shown in the pixel circuit of FIG. 4.

[0079] Hereinafter, a method for driving the OLED display having the above-mentioned emission control signal generating circuit in exemplary embodiments of the present invention will be described with reference to **FIG. 10**.

[0080] One frame is divided into four subframes in exemplary embodiments of the present invention, and scan signals are applied from the gate line driving circuit **510** to the gate lines during each subframe, so that  $4m$  scan signals are applied thereto during one frame. When the scan signal **S1** is applied to the first gate line **511** during the first subframe, the switching transistor **M51** is turned on to allow the R data signal **DR1** to be supplied from the data line **521** to the driving transistor **M52**.

[0081] In this case, the R emission control signal **EC\_R1'** is generated by the emission control signal generating circuit **590'** through the transfer gate **59-24** having the output control signal **OC** and the output control signal **OC** inverted from the inverting gate **59-22** as its control signals. As a result, when the emission control signal **EC\_R1'** is applied to the sequential control device **550'** to control the R EL element **EL\_R** in each of the pixels **P11'-P1n'** connected to the first gate line **511** through the emission control line **591r**, the thin film transistor **M55\_R'** is turned on to allow the driving current corresponding to the R data signals **DR1-DRn** to flow, respectively, through the R EL elements to be driven. In this case, since the ground voltage **Vss** is applied through the transfer gate **59-27** as the B emission control signals **EC\_B1-EC\_Bm**, the B EL elements are not driven.

[0082] When the second scan signal **S1** is applied to the first gate line **511** during the second subframe **2SF** of the first frame **1F**, the G data signals **DG1-DGn** are applied to the driving transistors **M52** of the pixels **P11'-P1n'** through the data lines **521-52n**, respectively. In this case, the emission control signal generating circuit **590'** generates the G emission control signal **EC\_G1'** from the shift register **59-21**, which is provided through the emission control line **591g**.

[0083] As such, when the emission control signal **EC\_G1'** is applied to the sequential control device **550'** to control the G EL elements **EL\_G** of the pixels **P11'-P1n'** connected to the first gate line **511**, the thin film transistors **M55\_G'** of the pixels **P11'-P1n'** are turned on to allow the driving current corresponding to the G data signals **DG1-DGn** to flow, respectively, through the G EL elements to be driven.

[0084] When the third scan signal **S1** is applied to the first gate line **511** during the third subframe **3SF** of the first frame **1F**, the B data signals **DB1-DBn** are applied to the driving transistors **M52** through the data lines **521-52n**, respectively. In this case, the emission control signal generating circuit **590'** generates the B emission control signal **EC\_B1'** to the emission control line **591b** through the transfer gate **59-26** in response to the output control signal **OC** and the output control signal **OC** inverted by the inverter **59-22**. Since the ground voltage **Vss** is supplied to the transfer gate **59-23** as the R emission control signals **EC\_R1'-EC\_Rm'**, the R EL element is not driven.

[0085] As such, when the emission control signal **EC\_B1'** is applied to the sequential control device **550'** to control the B EL elements **EL\_B** of the pixels **P11'-P1n'** connected to the first gate line **511**, the thin film transistors **M55\_B'** in the pixels are turned on to allow the driving current corresponding to the B data signals **DB1-DBn** to flow, respectively, through the B EL elements to be driven.

[0086] During the fourth subframe **4SF** of the first frame, the emission control signals generated from the sequential control device **550'** turn off the R and B EL elements, and have the driving current corresponding to black data to flow through the G EL element, which leads to have the black color displayed in the fourth subframe.

[0087] When the above-mentioned operation is repeated per each subframe of one frame to apply the scan signal to the  $m^{\text{th}}$  gate line **51m**, the R, G, B data signals (**DR1-DRn**, (**DG1-DGn**), (**DB1-DBn**) are sequentially applied to the data lines **521-52n**, and the emission control signals (**EC\_Rm'**, **EC\_Gm'**, **EC\_Bm'**) are sequentially generated by the emission control signal generating circuit **590'** to the sequential control device **550'**, which sequentially controls the R, G, B EL elements of the pixels **Pm1'-Pmn'** connected to the  $m^{\text{th}}$  gate line **51m** through the emission control lines **59mr**, **59mg**, **59mb**. As a result, the thin film transistors **M55\_R'**, **M55\_G'**, **M55\_B'** are sequentially turned on to thereby allow driving currents corresponding to the R, G, B data signals **DR1-DRn**, **DG1-DGn**, **DB1-DBn** to sequentially flow, respectively, through the R, G, B EL elements to be driven.

[0088] As such, whenever the scan signals **S1-Sm** are applied during each subframe of one frame, the data signals **DR1-DRn**, **DG1-DGn**, **DB1-DBn** are sequentially applied to the data lines, respectively, so that the R, G, B EL elements **EL\_R**, **EL\_G**, **EL\_B** of the pixel **P11'-Pmn'** are sequentially driven in a time-sharing manner.

[0089] The output control signal **OC** is supplied from an external source to the emission control signal generating circuit, and controls the R, G, B emission control signals to be output from the emission control signal generating circuit.

[0090] In accordance with a method for driving the OLED display in accordance with the second exemplary embodiment of the present invention, as shown in **FIG. 10**, one frame is divided into four subframes, and the R, G, B EL elements are sequentially driven by the R, G, B emission control signals generated from the emission control signal generating circuit **590'** per each of three subframes, and are driven by the R, G, B emission control signals to allow them to be in black color state during the rest subframe.

[0091] In accordance with another method for driving the OLED display of the second exemplary embodiment of the present invention, as shown in **FIG. 7**, one frame is divided into four subframes, and the R, G, B EL elements may be sequentially driven by the R, G, B emission control signals generated from the emission control signal generating circuit **590** per each of three subframes, and by the emission control signal generating circuit **590**, the G EL element of the R, G, B EL elements may be driven again during the rest subframe.

[0092] In accordance with the method for driving the OLED display of the present invention, the R, G, B emission control signals may be controlled to have a duty ratio of 50% to thereby reduce flicker and may be readily adjusted to thereby adjust white balance.

[0093] The emission control signal generating circuit of the present invention is applied to the OLED display which is sequentially driven per each subframe, however, it may be applied to the OLED display for driving the R, G, B EL elements using a plurality of emission control signals.

**[0094]** In the OLED display in accordance with the above-mentioned exemplary embodiments, the emission control signal generating circuit is formed to combine one shift register and a plurality of logic gates, which results in a simplified circuit configuration and a reduced circuit area. In addition, the duty ratio of the emission control signal may be adjusted to reduce the flicker and to adjust the white balance.

**[0095]** Further, the R, G, B EL elements share thin film transistors and a switching thin film transistor to be driven in a time-sharing manner, which implements the fine pitch, and the number of elements and interconnection lines may be reduced to improve the aperture ratio and the yield. In addition, RC delay and IR drop may be reduced.

**[0096]** While the present invention has been described with reference to certain exemplary embodiments, it should be understood that the disclosure has been made with the purpose of illustrating the invention by way of examples and is not intended to limit the scope of the invention. One skilled in the art would recognize that the described embodiments may be amended in various different ways without departing from the spirit or scope of the present invention. The scope of the present invention is indicated by the appended claims, and all changes that come within the meaning and range of equivalents thereof are intended to be embraced therein.

What is claimed is:

1. An emission control signal generating circuit of a flat panel display comprising a plurality of pixels, each said pixel including a plurality of EL elements, and emission of said elements being controlled by a plurality of emission control signals, the circuit comprising:

a first signal generating device for generating one of the plurality of emission control signals as an output signal; and

a plurality of second signal generating devices for generating other ones of the plurality of emission control signals using the output signal of the first signal generating device and an external control signal.

2. The circuit as claimed in claim 1, wherein the first signal generating device for generating said one of the plurality of emission control signals includes a shift register.

3. The circuit as claimed in claim 1, wherein one of the plurality of second signal generating devices includes a NAND gate having the external control signal and the output signal of the first signal generating device as two inputs, and another one of the plurality of second signal generating devices includes a NAND gate having an inverted signal of the external control signal and the output signal of the first signal generating device as two inputs.

4. The circuit as claimed in claim 1, wherein one of the plurality of second signal generating devices includes:

a first transfer gate for providing the output signal of the first signal generating device as one of said other ones of the plurality of emission control signals using the external control signal having a first level and an inverted signal of the external control signal having a second level; and

a second transfer gate for allowing said one of said other ones of the plurality of emission control signals to have the second level using the external control signal having the second level and the inverted signal of the external control signal having the first level.

5. The circuit as claimed in claim 4, wherein another one of the plurality of second signal generating devices includes:

a third transfer gate for providing the output signal of the first signal generating device as another one of said other ones of the plurality of emission control signals using the external control signal having the second level and the inverted signal of the external control signal having the first level; and

a fourth transfer gate for allowing said another one of said other ones of the plurality of emission control signals to have the second level using the external control signal having the first level and the inverted signal of the external control signal having the second level.

6. The circuit as claimed in claim 4, wherein the first level is a high logic level, and the second level is a low logic level.

7. The circuit as claimed in claim 5, wherein the first level is a high logic level, and the second level is a low logic level.

8. The circuit as claimed in claim 1, wherein the external control signal is an output control signal that controls the output of the emission control signal generating circuit, which is supplied from an external source.

9. The circuit as claimed in claim 1, wherein the plurality of EL elements are sequentially driven per each of a plurality of subframes that form one frame, and are in a black color state during one of the plurality of subframes.

10. The circuit as claimed in claim 1, wherein the plurality of EL elements are sequentially driven per each of subframes that form one frame, and one of the plurality of EL elements is driven again during one of the plurality of subframes.

11. An emission control signal generating circuit of an organic light emitting diode display comprising a plurality of pixels, each said pixel including R, G, B EL elements, emission of said elements being controlled by R, G, B emission control signals, the circuit comprising:

a shift register for generating the G emission control signal as an output signal;

a first NAND gate for generating the R emission control signal using the output signal of the shift register and an external control signal as two inputs;

an inverting gate for inverting the external control signal to generate an inverted external control signal; and

a second NAND gate for generating the B emission control signal using the inverted external control signal and the output signal of the shift register as two inputs.

12. The circuit as claimed in claim 11, wherein the R, G, B EL elements are sequentially driven per each of a plurality of subframes that form one frame, and the R, G, B EL elements are in a black color state or one of the R, G, B EL elements is driven again during one of the plurality of subframes.

13. An emission control signal generating circuit of an organic light emitting diode display comprising a plurality of pixels, each said pixel including R, G, B EL elements, and emission of said elements being controlled by R, G, B emission control signals, the circuit comprising:

an inverting gate for inverting an external control signal to generate an inverted external control signal;

a shift register for generating the G emission control signal as an output signal;

a first transfer gate for transferring the output signal of the shift register as the R emission control signal using the inverted external control signal and the external control signal;

a second transfer gate for grounding the R emission control signal using the inverted external control signal and the external control signal;

a third transfer gate for transferring the output signal of the shift register as the B emission control signal using the inverted external control signal and the external control signal; and

a fourth transfer gate for grounding the B emission control signal using the inverted external control signal and the external control signal.

**14.** The circuit as claimed in claim 13, wherein the R, G, B EL elements are sequentially driven per each of a plurality of subframes that form one frame, and the plurality of EL elements are in a black color state or one of the plurality of EL elements is driven again during one of the plurality of subframes.

**15.** An organic light emitting diode display, comprising:

a plurality of gate lines, a plurality of data lines, a plurality of emission control lines, and a plurality of power supply lines;

a pixel portion including a plurality of pixels, each said pixel being connected to a corresponding said gate line, a corresponding said data line, a corresponding said emission control line and a corresponding said power supply line;

a gate line driving circuit for supplying the plurality of gate lines with a plurality of scan signals;

a data line driving circuit for sequentially supplying the plurality of data lines with R, G, B data signals; and

an emission control signal generating circuit for supplying the plurality of emission control lines with a plurality of emission control signals,

wherein each said pixel includes R, G, B EL elements, which sequentially emit light based on the emission control signals per each of a plurality of subframes that form one frame, and

wherein the emission control signal generating circuit includes:

a first signal generating device for generating one of the plurality of emission control signals as an output signal; and

a plurality of second signal generating devices for generating other ones of the plurality of emission control signals using the output signal of the first signal generating device and an external control signal.

**16.** The organic light emitting diode display as claimed in claim 15, wherein the first signal generating device includes a shift register.

**17.** The organic light emitting diode display as claimed in claim 15, wherein one of the plurality of second signal generating devices includes a NAND gate having the external control signal and the output signal of the first signal generating device as two inputs, and another one of the plurality of second signal generating devices includes a NAND gate having an inverted signal of the external control signal and the output signal of the first signal generating device as two inputs.

**18.** The organic light emitting diode display as claimed in claim 15, wherein one of the plurality of second signal generating devices includes:

a first transfer gate for providing the output signal of the first signal generating device as one of said other ones of the plurality of emission control signals using the external control signal having a first level and an inverted signal of the external control signal having a second level; and

a second transfer gate for allowing said one of said other ones of the plurality of emission control signals to have the second level using the external control signal having the second level and the inverted signal of the external control signal having the first level, and

wherein another one of the plurality of second signal generating devices includes:

a third transfer gate for providing the output signal of the first signal generating device as another one of said other ones of the plurality of emission control signals using the external control signal having the second level and the inverted signal of the external control signal having the first level; and

a fourth transfer gate for allowing said another one of said other ones of the plurality of the emission control signals to have the second level using the external control signal having the first level and the inverted signal of the external control signal having the second level.

**19.** The organic light emitting diode display as claimed in claim 18, wherein the first level is a high logic level, and the second level is a low logic level, and the external control signal is an output control signal that controls an output of the emission control signal generating circuit, which is supplied from an external source.

**20.** The organic light emitting diode display as claimed in claim 15, wherein the R, G, B EL elements are sequentially driven per each of a plurality of subframes that form one frame, and the R, G, B EL elements are in a black color or one of the R, G, B EL elements is driven again during one of the plurality of subframes.

**21.** The organic light emitting diode display as claimed in claim 18, wherein each said pixel further includes:

at least one switching transistor for switching a data signal;

at least one driving transistor for providing the R, G, B EL elements with a driving current corresponding to the data signal;

a capacitor for storing the data signal; and

a sequential control device for controlling sequential driving of the R, G, B EL elements.

**22.** The organic light emitting diode display as claimed in claim 21, wherein the sequential control device includes first, second and third P-type thin film transistors, each said thin film transistor including a gate to which a corresponding said emission control signal is applied, a source connected to the driving device in common, and a drain connected to a corresponding one of the R, G, B EL elements.

**23.** The organic light emitting diode display as claimed in claim 21, wherein the sequential control device includes a first N-type thin film transistor, a first P-type thin film transistor and a second N-type thin film transistor, each said thin film transistor including a gate to which a corresponding said emission control signal is applied, a source connected

to the driving device in common, and a drain connected to a corresponding one of the R, G, B EL elements.

**24. An organic light emitting diode display, comprising:**

a plurality of gate lines, a plurality of data lines, a plurality of emission control lines, and a plurality of power supply lines;

a pixel portion including a plurality of pixels, each said pixel being connected to a corresponding said gate line, a corresponding said data line, a corresponding said emission control line and a corresponding said power supply line;

a gate line driving circuit for supplying the plurality of gate lines with a plurality of scan signals;

a data line driving circuit for sequentially supplying the plurality of data lines with R, G, B data signals; and an emission control signal generating circuit for supplying the plurality of emission control lines with R, G, B emission control signals,

wherein each said pixel includes R, G, B EL elements, which sequentially emit light based on the R, G, B emission control signals per each of a plurality of subframes that form one frame, and

wherein the emission control signal generating circuit includes:

a shift register for generating the G emission control signal as an output signal;

a first NAND gate for generating the R emission control signal using the output signal of the shift register and an external control signal as two inputs;

an inverting gate for inverting the external control signal to generate an inverted external control signal; and

a second NAND gate for generating the B emission control signal using the inverted external control signal and the output signal of the shift register as two inputs.

**25. An organic light emitting diode display, comprising:**

a plurality of gate lines, a plurality of data lines, a plurality of emission control lines, and a plurality of power supply lines;

a pixel portion including a plurality of pixels, each said pixel being connected to a corresponding said gate line, a corresponding said data line, a corresponding said emission control line and a corresponding said power supply line;

a gate line driving circuit for supplying the plurality of gate lines with a plurality of scan signals;

a data line driving circuit for sequentially supplying the plurality of data lines with R, G, B data signals; and

an emission control signal generating circuit for supplying the plurality of emission control lines with R, G, B emission control signals,

wherein each said pixel includes R, G, B EL elements, which sequentially emit light based on the R, G, B emission control signals per each of a plurality of subframes that form one frame, and

wherein the emission control signal generating circuit includes:

an inverting gate for inverting an external control signal to generate an inverted external control signal;

a shift register for generating the G emission control signal as an output signal;

a first transfer gate for transferring the output signal of the shift register as the R emission control signal using the inverted external control signal and the external control signal;

a second transfer gate for grounding the R emission control signal using the inverted external control signal and the external control signal;

a third transfer gate for transferring the output signal of the shift register as the B emission control signal using the inverted external control signal and the external control signal; and

a fourth transfer gate for grounding the B emission control signal using the inverted external control signal and the external control signal.

**26. A method for driving an organic light emitting diode display comprising a plurality of pixels, each said pixel including R, G, B EL elements, emission of said elements being controlled by R, G, B emission control signals, the method comprising:**

generating the G emission control signal during a first subframe among a plurality of subframes that form one frame to emit the G EL element;

generating the R emission control signal using the G emission control signal during a second said subframe to emit the R EL element;

generating the B emission control signal using the G emission control signal during a third said subframe to emit the B EL element; and

maintaining the EL elements to be a black color during a rest subframe among the plurality of subframes.

**27. A method for driving an organic light emitting diode display comprising a plurality of pixels, each said pixel including R, G, B EL elements, emission of said elements being controlled by R, G, B emission control signals, the method comprising:**

generating the G emission control signal during a first subframe among a plurality of subframes that form one frame to emit the G EL element;

generating the R emission control signal using the G emission control signal during a second said subframe to emit the R EL element;

generating the B emission control signal using the G emission control signal during a third said subframe to emit the B EL element; and

emitting one of the R, G, B EL elements during a rest subframe among the plurality of subframes.

|                |                                                                                           |         |            |

|----------------|-------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | Amoled显示器及其驱动方法                                                                           |         |            |

| 公开(公告)号        | <a href="#">US20050116656A1</a>                                                           | 公开(公告)日 | 2005-06-02 |

| 申请号            | US10/985795                                                                               | 申请日     | 2004-11-11 |

| [标]申请(专利权)人(译) | SHIN董勇                                                                                    |         |            |

| 申请(专利权)人(译)    | 申东勇                                                                                       |         |            |

| 当前申请(专利权)人(译)  | 三星DISPLAY CO. , LTD.                                                                      |         |            |

| [标]发明人         | SHIN DONG YONG                                                                            |         |            |

| 发明人            | SHIN, DONG-YONG                                                                           |         |            |

| IPC分类号         | H01L51/50 G09G3/10 G09G3/20 G09G3/30 G09G3/32 H05B33/00 H05B33/14                         |         |            |

| CPC分类号         | G09G3/3233 G09G3/3266 G09G2300/0804 G09G2330/025 G09G2300/0861 G09G2310/061 G09G2300/0842 |         |            |

| 优先权            | 1020030084779 2003-11-27 KR                                                               |         |            |

| 其他公开文献         | US8872736                                                                                 |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">USPTO</a>                                           |         |            |

### 摘要(译)

用于控制R, G, B EL元件发光的发光控制电路和使用该发光控制电路驱动有机发光二极管显示器的方法。平板显示器的发光控制信号产生电路包括多个像素。每个像素包括多个EL元件，并且元件的发射由发射控制信号控制。该电路包括：第一信号发生装置，用于产生发射控制信号之一；以及多个第二信号发生装置，用于使用第一信号发生装置的输出信号和外部控制信号产生其他发射控制信号。第一信号发生装置可以包括移位寄存器。多个第二信号发生装置中的每一个可以包括使用外部信号和外部控制信号或其反相信号的NAND门作为两个输入。